## Electromagnetic Coupling Effects in RFCMOS Circuits

A.O.Adan, M. Fukumi, K. Higashi, T. Suyama<sup>+</sup>, M. Miyamoto<sup>+</sup>, M. Hayashi

IC Development Group, SHARP Corp., 2613-1, Ichinomoto-cho, Tenri, Nara, JAPAN

<sup>+</sup>Advanced Research Labs., SHARP Corp., 2613-1, Ichinomoto-cho, Tenri, Nara, JAPAN

**Abstract:** The electromagnetic isolation and coupling characteristics of basic structures, namely metal pads, spiral inductors, and spiral-transistors, implemented in a core-logic CMOS process are evaluated and modeled. The models provide design guidelines on the isolation characteristics of guard-rings and shield layers for RF cross-talk suppression between circuit blocks. The importance of electromagnetic coupling to layout interconnects is demonstrated.

### I. INTRODUCTION

Integration of RF transceiver circuits in core CMOS process is actively pursued [1] in an effort to increase functionality and reduce cost. In mixed mode Logic-RF IC's digital switching noise coupled through the substrate, as well as electromagnetic coupling (EMC) between RF circuit blocks is a concern, and several papers have reported these effects [2, 3]. However, solutions have been proposed like the use of deep trenches [2], or the use of SOI substrate [4], which are not compatible with standard CMOS.

In this work, the measured and modeled RF interaction characteristics of basic structures, namely metal pads, spiral inductors, and spiral-transistors, implemented in a core-logic CMOS process are evaluated. Furthermore, the effects of shielding layers (P+ diffusion) and guard rings are presented. These simple test structures give insight in the coupling mechanisms and allow the derivation of guidelines to reduce EMC effects.

The experimental evaluation was conducted on a standard 0.25um, 4-level Metal, logic-CMOS process on 10Ω.cm p-type bulk wafers. The process features standard twin-wells and Shallow Trench Isolation.

### II. PADS CAPACITIVE COUPLING

The simplest EM couplings to the substrate are due to capacitive interaction of metal pads or metal

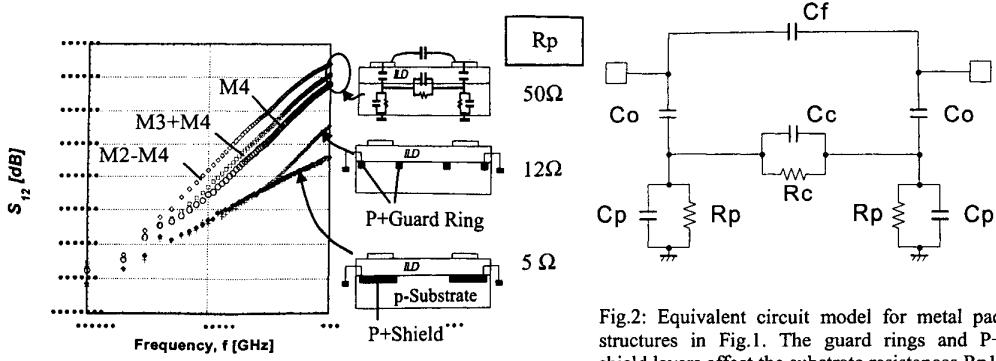

interconnects and injection by well ties and pn diffusions. Fig.1 shows the metal pad-to-pad structures and the measured magnitude of coupling  $S_{21}$  versus frequency. The pad spacing and size are 100um and 100um x 100um, respectively. The metal pad is coupled to the substrate capacitively. These effects can be well modeled by the equivalent circuit shown in Fig.2, where  $C_o$ 's are the ILD capacitances,  $R_p$ ,  $C_p$  are the substrate resistance and capacitance to ground, and  $R_c$ ,  $C_c$  are the substrate lateral coupling resistance and capacitance, respectively. The guard ring and the P+ grounded layer underneath the pad modify the substrate resistances  $R_p$ . In Fig.1, using different metal stacks varied the ILD capacitance effect. Using a P+ grounded shield underneath the pad or a P+ guard ring are the most effective ways to suppress coupling. At 2GHz, ~17dB reduction in  $S_{21}$  is achieved by the P+ grounded shield layer, as compared with the non-shielded pad. As the model shows, the guard ring and shielding layers act reducing EMC by shorting out the substrate resistances  $R_p$ . The extracted  $R_p$  values are 50Ω, 12Ω and 5Ω for the reference, the P+ guard ring and the P+ grounded shield, respectively.

### III. SPIRAL-TO-SPIRAL COUPLING

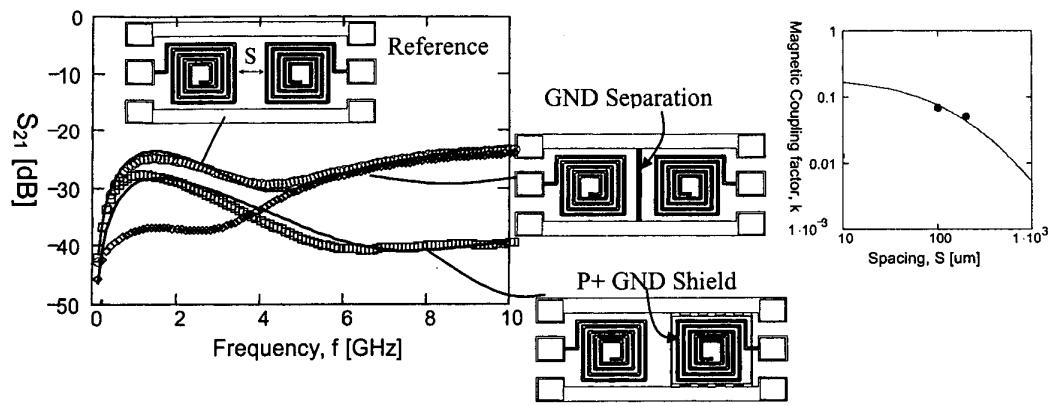

Planar spiral inductors occupy a large Si area and are widely used in RF circuits. The EMC of planar spiral inductors must be modeled to determine the effect on gain and reverse isolation of amplifiers [3], as well as between large signal circuit blocks (output amp) and sensitive Low-Noise Amplifiers (LNA). The spiral coupling was studied using the patterns in Fig.3. The spiral inductors are 100um separated and have a length of 3810um,  $L=6.3nH$ , with metal width and spacing of 15um and 5um, respectively. The isolation effects of (1) a grounded P+ diffusion-top metal barrier in between the inductors and (2) Salicided P+ grounded shield underneath one of the

Fig.1: EM coupling  $S_{21}$  between metal pads and the effect of guard rings and P+ grounded shields. The extracted substrate resistances  $R_p$  are indicated.

Fig.2: Equivalent circuit model for metal pad structures in Fig.1. The guard rings and P+ shield layers affect the substrate resistances  $R_p1$ ,  $R_p2$  and  $R_c$ .

Fig.3: Measured (symbols) and model calculated (lines) magnetic coupling  $k$  and  $S_{21}$  for EM coupling between planar spiral inductors on bulk-Si  $10\Omega\cdot\text{cm}$  p-substrate. The spirals spacing is  $S=100\mu\text{m}$ . The GND separation is a P+ grounded diffusion-Top metal barrier between the spirals. The P+GND shield is a salicided P+ diffusion layer underneath the right-side spiral.

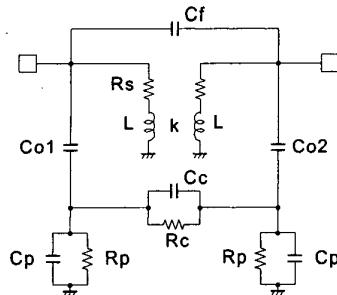

Fig.4: Equivalent circuit for Spiral-to-Spiral coupling.

Table I: Model Parameters Extracted for Spirals Coupling

| Parameter | Unit     | Reference | GND Separation | P+GND Shield |

|-----------|----------|-----------|----------------|--------------|

| $L$       | nH       | 6.3       | ↔              | ↔            |

| $R_s$     | $\Omega$ | 8         | ↔              | ↔            |

| $k$       |          | 0.07      | 0.015          | 0.04         |

| $R_{p1}$  | $\Omega$ | 29        | 28             | 25           |

| $R_{p2}$  | $\Omega$ | 29        | 28             | 3            |

| $C_p$     | fF       | 200       | ↔              | ↔            |

| $R_c$     | $\Omega$ | 73        | 110            | 73           |

| $C_c$     | fF       | 10        | 1              | 10           |

| $C_o$     | fF       | 320       | ↔              | ↔            |

| $C_f$     | fF       | 20        | ↔              | ↔            |

inductors were evaluated to gain insight into the coupling mechanisms. Fig.4 shows the proposed circuit model to analyze the EMC. In Fig.3, the measured (symbols) and calculated (lines) frequency response of  $S_{21}$  for the three structures, and the magnetic coupling factor  $k$  for the reference pair of spirals are reported. Good agreement is observed between the model results and measurements. The model parameters are summarized in Table I. A maximum  $S_{21}$  of  $\sim -25$ dB is observed at 1.5 GHz for the reference pattern. At low frequencies, magnetic coupling ( $k$ ) dominates spiral isolation. The grounded P+ diffusion-top metal separation effectively reduces  $S_{21}$  to  $\sim -37$ dB at 1.5GHz. At high frequencies, the substrate coupling resistance ( $R_c$ ) is dominant, however, a grounded shield underneath the spiral completely shorts out the coupling to  $S_{21} = -40$ dB.

From the model and the experimental results, the effectiveness of each structure can be assessed.

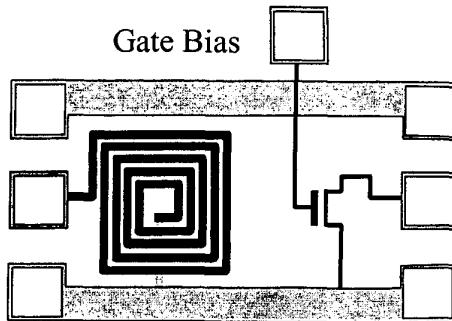

#### IV. SPIRAL-TO-TRANSISTOR COUPLING

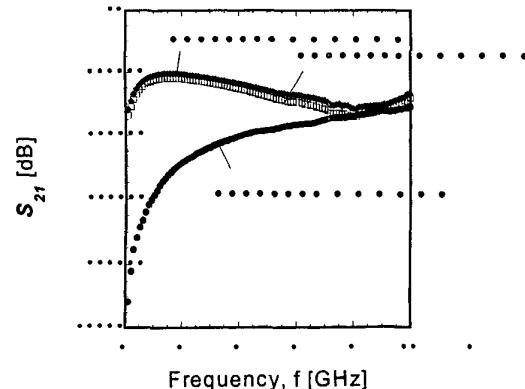

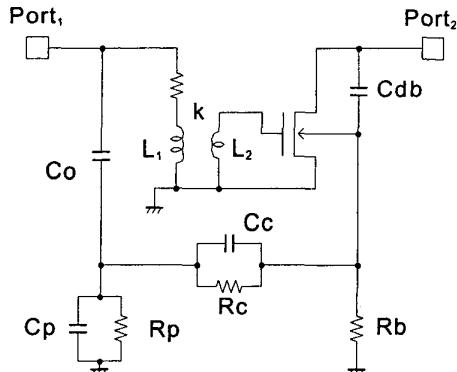

Due to its large area, the spiral inductor can couple significant EM energy not only to other spirals but also to sensitive transistors. Fig.5 shows the new test structure proposed to evaluate this effect. This structure is used to emulate the situation that might arise, for example, in the interference between the transmitter and receiver paths of a RF transceiver. Fig.6 illustrates the measured  $S_{21}$  at the transistor's drain terminal, and with bias current as parameter. The general shape of  $S_{12}$ -vs- $f$  is similar to that for the spiral-spiral coupling structure. An equivalent circuit is proposed in the Fig.7.

The magnetic coupling between the spiral and the layout parasitics of the transistor, especially the gate bias interconnect line, can be studied using the equivalent circuit model. When the substrate coupling is neglected ( $R_p=0$ ,  $C_c=0$ ,  $R_c \rightarrow \infty$ ),

$$\begin{aligned} |S_{21}(\omega)| &\equiv 2 g_m M \omega & \omega \rightarrow 0, \\ |S_{21}(\omega)| &\equiv \frac{2 g_m M}{\omega^3 L_1 L_2 C_g (C_o + C_{gd})} & \omega \rightarrow \infty \end{aligned} \quad (1)$$

where  $L_1$ ,  $L_2$  and  $M = k \sqrt{L_1 L_2}$  are the spiral inductor, gate line parasitic inductance, and the mutual inductance, respectively, and  $g_m$  is the

transistor transconductance. The coupling coefficient is  $k \sim 0.05$  as estimated from layout. At low frequencies, the  $S_{21}$  increases due to the magnetic coupling, and the amplification action of the transistor. As frequency increases  $S_{21}$  decreases since the gate capacitance of the transistor,  $C_g$ , shorts the coupling to ground. As a result of the two behaviors described by (1), a peak is seen in the  $S_{21}$  characteristic. At further high frequencies, the substrate capacitively and resistively couples the interference to the interconnect lines, the back gate of the transistor, and the drain-substrate capacitance of the transistor.

These results clearly show how the transistor action amplifies the coupled interference which results in  $S_{21} \sim -20$ dB at 1.5GHz, i.e. stronger effect than in the passive spiral-spiral coupling of Fig.3. When the transistor is OFF ( $I_d=0$ mA curve), the capacitive coupling to the substrate ( $C_o$ ,  $C_{db}$ ) and transmission through the substrate ( $R_c$ ,  $C_c$ ) are similar to the effect reported in Fig.1 for the metal pads EMC. This test structure demonstrates the importance of modeling EMC effects between passive components; interconnect lines, and active circuits.

#### V. CONCLUSION

Characterization and analysis of the EMC effects of basic structures (metal pads, spiral-spiral and spiral-to-transistor), implemented on a standard logic CMOS process on p-type bulk wafers, were described. Compared with previous reports, a comprehensive equivalent circuit modeling was introduced and validated with measured data. The effect and effectiveness of different guard rings, and P+ grounded shield layers were also studied. From these results, it is observed that not only the substrate, but also the electromagnetic coupling to layout interconnect must be considered in the characterization and minimization of EMC at radio frequencies.

Fig.5: Test pattern to evaluate Spiral-Transistor EM coupling. Transistor: L=0.25um, W=60 fingers x 5um.

Fig.6: Measured coupling  $S_{21}$  of the Spiral-Transistor structure at different bias conditions.

Fig.7: Proposed equivalent circuit of the Spiral-Transistor coupling.

$L_1$ : Planar spiral inductance,  $L_2$ : parasitic inductance of the gate bias line,  $k$ : magnetic coupling factor,  $R_b$ : Transistor equivalent body resistance,  $C_{db}$ : transistor drain-substrate junction capacitance.  $C_o$ : Spiral to substrate (ILD) capacitance,  $R_p$ ,  $C_p$ : substrate resistance and capacitance to ground, respectively,  $R_c$ ,  $C_c$ : substrate coupling resistance and capacitance, respectively.

#### REFERENCES

- [1] H. Samavati, H.R. Rategh, and T.H. Lee, "A fully-integrated 5GHz CMOS wireless-LAN receiver", ISSCC Dig. Tech. Papers, pp. 208-209, Feb. 2001.

- [2] C.S.Kim, P. Park, J-W. Park, N. Hwang, and H.K. Yu, "Deep trench guard technology to suppress coupling between inductors in silicon RF ICs", IEEE MMT-S Symposium Digest, 2001.

- [3] A.L.L. Pun, T. Yeung, K. Lau, F.J.R. Clement, and D.K. Su, "Substrate noise coupling through planar spiral inductor", IEEE J. Solid-State Circuits, vol.33, No.6, pp.877-884, Jun.1998.

- [4] J.S. Hamel, S. Stefanou, M. Bain, B.M. Armstrong, and H.S. Gamble, "Substrate crosstalk suppression capability of Silicon-on-Insulator substrates with buried ground planes (GPSOI)", IEEE Microwave and Guided Wave Lett., vol.10, No.4, pp. 134-135, Apr. 2000.